触摸按键不灵敏?可能是PCB布局出了问题!

在日常使用电子产品时,触摸按键不灵敏的问题时有发生。用户可能会疑惑:是硬件故障、软件调试问题,还是设计缺陷?其实,PCB布局的细节可能正是影响触摸灵敏度的关键因素之一。

一、PCB布局如何影响触摸灵敏度?

1. 基准电容:布局中的“隐形门槛”

触摸按键的核心原理是检测手指触摸时产生的电容变化。PCB布局会直接影响基准电容(即未触摸时的初始电容值),而基准电容的大小与灵敏度密切相关。

极板面积与距离:基准电容量与极板面积成正比,与极板间距成反比。若感应焊盘面积过大、铺地比例过高,或走线过长,都可能抬高基准电容,导致手指触摸时的电容变化率(C%)被稀释,灵敏度下降。

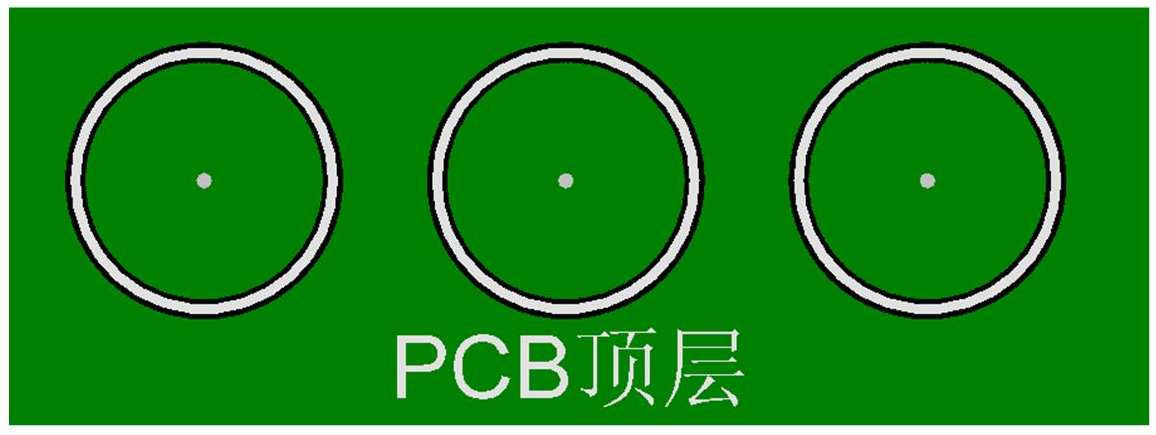

铺地形式与间距:

顶层铺地建议采用网格地,且需与感应盘保持0.75mm以上距离;

底层铺地推荐网格地,铜面积占比不超过30%,并与感应盘保持安全间距;

单面板铺地需全实铜,但同样需与感应盘保持0.75mm间距。

2. 干扰源:隐藏的“灵敏度杀手”

PCB布局不当可能引入多种干扰,直接影响触摸信号的稳定性:

电源干扰:若触摸芯片采用开关电源,其纹波可能干扰芯片工作。建议优先使用线性电源,或通过LDO(如5PIN LDO)进行稳压。

元件布局:

触摸芯片位置需合理:单面板布局时,芯片应尽量靠近触摸板中心,以平衡各通道引脚到感应盘的距离;双面板布局时,芯片及相关元件建议放在底层,并靠近感应按键。

通道匹配电阻和灵敏度调节电容需紧贴IC放置,以减少信号干扰。

3. 走线设计:细节决定体验

感应盘到IC的走线是触摸信号传输的“最后一公里”,其设计直接影响灵敏度:

走线原则:连线需尽量细、短,避免与其他信号线平行或交叉,以防止串扰。

走线位置:优先将连线布局在PCB底层,并避免跨越高频、强干扰信号线。

二、布局优化:从问题到解决方案

1. 减小基准电容的实战技巧

优化感应焊盘尺寸,避免过度铺地;

采用网格地替代实心铺地,降低极板面积;

缩短感应走线长度,减少信号传输路径。

2. 抗干扰设计的关键措施

电源优化:为触摸芯片单独配置LDO,隔离电源纹波;

元件布局:将稳压电路、滤波电容等紧邻触摸芯片放置,形成局部稳定电源域;

屏蔽设计:在干扰源(如高频信号线)附近增加屏蔽层或隔离带。

3. 走线优化的具体建议

感应盘到IC的走线宽度控制在0.2mm以内(具体需根据产品尺寸调整);

避免走线经过开关电源、电机驱动等强干扰区域;

若必须跨越干扰区域,可采用差分走线或增加屏蔽线。

三、总结:布局无小事,细节见真章

触摸按键的灵敏度问题,往往与PCB布局的“隐性缺陷”密切相关。通过合理控制基准电容、规避干扰源、优化走线设计,可以有效提升触摸体验。在实际工程中,建议结合仿真工具验证布局效果,并通过多次迭代优化设计。毕竟,在电子设计中,没有“一劳永逸”的方案,只有不断逼近完美的细节打磨。如有需求欢迎联系我们!